|

Use the I/O Pin Planning layout to perform pin assignments in a design.Ĭustomize IP, instantiate IP, and verify the hierarchy of your design IP. Reviews creating timing constraints according to the design scenario, synthesizing and implementing the design, and, optionally, generating and downloading a bitstream to a demo board. It is just a very introductory example for students, implementing an 'and' and an 'or' gate, and connecting the input and output to buttons and LEDs. It includes: Design Entry, Synthesis, Place and Route, Verification/Simulation tools. C:XilinxVivado2021.1databoardsboardfiles Everything seemed to work for a simple design. Vivado Synthesis, Implementation, and Bitstream Generation Vivado is the design software for AMD adaptive SoCs and FPGAs.

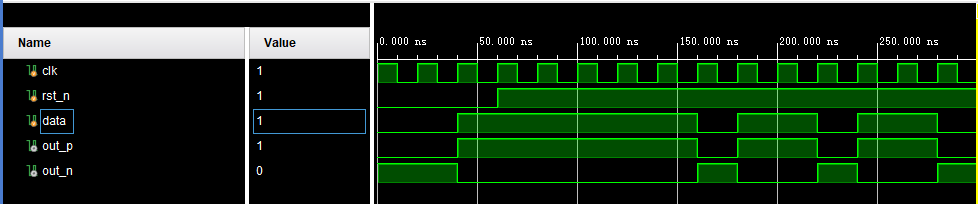

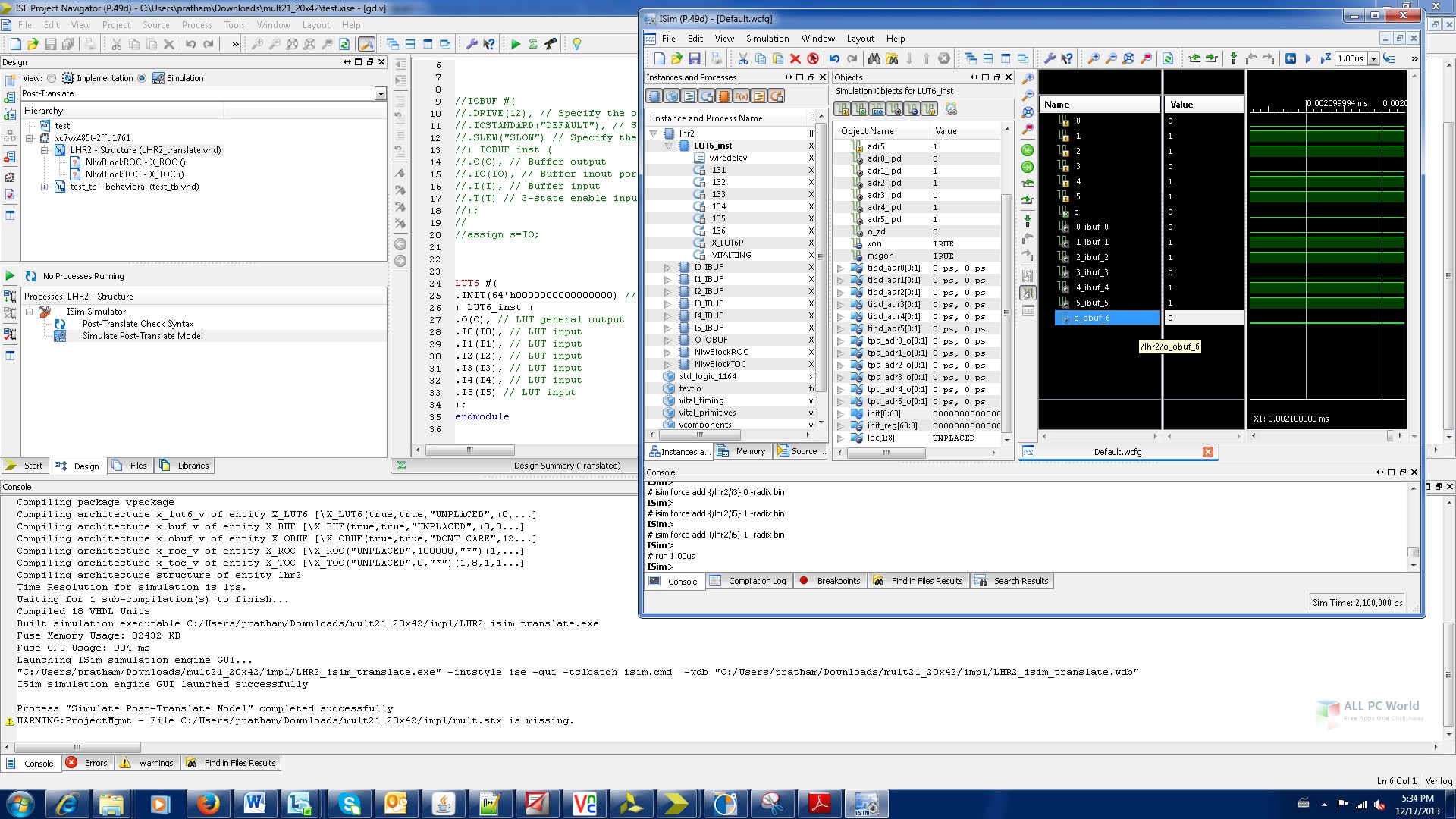

Introduces the methodology guidelines covered in this course and the UltraFast Design Methodology checklist.Ĭovers RTL and the RTL design flow, recommended coding guidelines, using control signals, and recommendations on resets.ĭescribes the process of behavioral simulation and the simulation options available in the Vivado IDE. UltraFast Design Methodology: Board and Device Planning Solution: the problem disappeared when I copied the three dll files from C: to C. I discovered that a few of the 2020.3 files were still there after the rollback. Once driver uninstall completed please disconnect the programming cable. When the uninstall dialog popped up then checked the box that says Delete the driver software for this device.

Vivado Design Suite Non-Project Based Modeĭescribes the design flow using non-project batch mode, including using design analysis commands and how constraints are managed in non-project mode. The next day it complained that the three dll files were missing. Software Development Kit (SDK) Zynq UltraScale+ MPSoC, Zynq 7000 SoCs, and MicroBlaze support. Go to device manager> Right click on Platform USB in the device manager and click Uninstall. By default this folder contains XML files for different FPGA boards manufactured by Xilinx. Introduces the project-based flow in the Vivado Design Suite: creating a project, adding files to the project, exploring the Vivado IDE, and simulating the design. After installing Vivado, the default installation directory on your drive will contain a folder called boardfiles.If Vivado is installed in the C drive ( usually recommended ), then the boardfiles folder can be found here: C:XilinxVivado2015.1databoards.

Introduces 7 series and UltraScale™ FPGAs, stacked silicon interconnect-based 3D IC devices, Zynq™ 7000 SoCs, Zynq UltraScale+™ MPSoCs, and Versal™ adaptive SoCs.ĭescribes various design flows and the role of the Vivado IDE in the flows.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed